Librery 25/06/16

Duration: 3 hours

EE306

Marks: 100

### BHARATIYA VIDYA BHAVAN'S

# SARDAR PATEL COLLEGE OF ENGINEERING

Munshi Nagar, Andheri (West), Mumbai 400 058

(A Government Aided Autonomous Institute)

### KT EXAM

**COURSE: POWER ELECTRONICS**

Class/Branch: T.E./ELECTRICAL

June 2016

Semester: V

### Note:

- Solve any 5 questions from remaining 7 questions

- Assume suitable data if required.

- Figures to right indicate full marks.

- Answers to all sub-questions should be grouped together.

Master file.

| Ql)<br>a) |    | Draw the output voltage waveform of three phase half wave uncontrolled converter with resistive load. And derive Average output voltage.     | 10     |

|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------|--------|

| b)        |    | Draw and explain turn off characteristic of Silicon controlled rectifier.                                                                    | 10     |

| Q2)       | a) | In Buck regulator find critical values of <b>inductor</b> & <b>capacitor</b> for continuous inductor current and capacitor voltage.          | 5<br>5 |

|           | b) | With the help of neat circuit explain single phase dual converter.  Wwhich type of load this converter is used?                              | 8<br>2 |

| Q3)       | a) | Explain the effect of source inductance on rectifiers.                                                                                       | 10     |

|           | b) | What is principle of operation of step down dc to dc converter?                                                                              | 10     |

|           |    | . 194                                                                                                                                        |        |

| Q4)       | a) | Explain natural or line commutation.                                                                                                         | 10     |

|           | b) | Compare voltage source inverter & current source inverter.                                                                                   | 10     |

| Q5)       | a) | Derive expression of average dc voltage for the three phase full wave uncontrolled rectifier.  Assume load current is continuous & constant. | 10     |

|     | b) | Draw output voltage and load current waveforms of full bridge single phase VSI with R-L load. (only waveforms are expected)                                                                                  | 8   |

|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Q6) | a) | Draw output voltage and load current waveform of 1 phase full wave bridge ,controlled rectifier with R-L-E load and $\alpha=60^\circ$ Assume load current is continuous and constant. Justify your waveforms | 8 2 |

|     | b) | Explain single phase sine triangular wave PWM technique used for inverters using following pts -why pwm -circuit dia -waveform                                                                               | 10  |

| Q7) | a) | Draw output voltage and load current waveforms of single phase full wave uncontrolled rectifier with pure 'L' load.(only waveforms are expected)                                                             | 8   |

|     | b) | Draw output voltage and load current waveforms of 1 phase half bridge voltage source inverter connected to following loads. Justify waveforms.  1. Pure L  2. R-I-F                                          | 12  |

and the second s

1.0

24/06/16

Bharatiya Vidya Bhavan's

# Sardar Patel College of Engineering

(A Government Aided Autonomous Institute) Munshi Nagar, Andheri (West), Mumbai - 400058. KT Exam June 2016

Max. Marks: 100

Class: T.Y. B.Tech.

Semester: V

Name of the course: Digital System Design

Q. P. Code:

Duration: 3Hrs.

Program: Electrical

Course Code: EE305

**Instructions:**

Q1 is compulsory.

Solve any four questions from the remaining six questions.

Master file.

| Q    |                                                                                                                                                                                                                                                                                                                     | Max<br>Marks                            | Course<br>Outcome | Module<br>Number |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------|------------------|

| No   |                                                                                                                                                                                                                                                                                                                     | , , , , , , , , , , , , , , , , , , , , | Number            |                  |

| QIa  | The hypothetical synchronous machine has 8 bits data bus and 16 bits address bus with lower address byte time multiplexed with data bus. It is interfaced with 64kbyte read write memory chip. The input clock frequency is 10MHz. Show the connection diagram between processor and memory chip for data transfer. | 04                                      | COI               | 01               |

| b    | How can the performance equation of the machine be improved?                                                                                                                                                                                                                                                        | 04                                      | CO2               | 01               |

| e    | Explain difference between inertial and transport delay.                                                                                                                                                                                                                                                            | 04                                      | CO4               | 5                |

| d    | Explain the following statements in VHDL.  (i) Loop (ii) Next  (iii) Exit (iv) Wait.                                                                                                                                                                                                                                | 04                                      | CO4               | 5                |

| e    | Why are the peripherals not connected directly to system bus?                                                                                                                                                                                                                                                       | 04                                      | CO3               | 5                |

| Q2 a | List and briefly explain different addressing modes.                                                                                                                                                                                                                                                                | 10                                      | CO2               | 2                |

| b    | With examples explain different types of instructions.                                                                                                                                                                                                                                                              | 10                                      | CO2               | 2                |

| Q3 a | Explain the concept of eache memory with all possible approaches to eache coherency.                                                                                                                                                                                                                                | 10                                      | CO3               | 3                |

| b    | With a neat diagram explain set associative mapping.                                                                                                                                                                                                                                                                | 10                                      | CO3               | 3                |

| Q4 a | With a help of neat block diagram explain the concept of DMA and its transfer.                                                                                                                                                                                                                                      | 10                                      | CO3               | 4                |

| b            | Explain various steps taken by CPU in interrupt handling process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 05  | CO3   | 4   |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|

| c            | List and explain two types of I/O interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 05  | CO3   | 4   |

| Q5 a         | Write VHDL code to implement 8-bit latch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 05  | C.O.1 | 5,6 |

| b            | Write different modeling styles in VIIDL using an example of 4:1 multiplexer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10  | CO4   | 5,6 |

| e            | Draw structural model of full adder circuit and write VHDL code to analyze the same.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 05  | CO4   | 5,6 |

| Q6 a         | Write VHDL code to implement SR flip flop with rising clock edge. Make use of 'process'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10  | CO4   | 5,7 |

| b            | AND THE ACCURACY OF THE CONTRACT OF THE CONTRA | 11) | CO4   | 5,7 |

| <b>Q</b> 7 a | List and briefly define the major types of Operating System scheduling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 05  | CO3   | 4   |

| b            | Why the unequal fixed size and variable size partitions are are inefficient? Explain paging system in detail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10  | CO3   | 4   |

| c            | Compare RISC and CISC Computers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 05  | CO1   | 1   |

## Bharatiya Vidya Bhavan's

# Sardar Patel College of Engineering

## K.T.-Examination

June- 2016

Max. Marks: 100

Class: T.Y. B. Tech

Semester: V

Name of the Course: Electrical machines-II

Instructions:

**Duration:** 3 Hour

Program: B. Tech

Course Code: EE 303

MASTER FILE

1. Attempt any questions

Draw neat diagrams

3. Assume suitable data if necessary and justify the same.

| Ques.<br>No |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Max.<br>Marks |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Q1. (a)     | What is the need of lagging power factor operation of synchronous generator?                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 06            |

| (b)         | Explain in brief the armature reaction in case of synchronous generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 08            |

| (c)         | "Explain why single phase Induction Motor is not a self start motor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 06            |

| Q2(a)       | Explain why single phase resolution of voltage regulation by: (i) EMF (ii) MMF and (iii) ZPF method. Take armature resistance into account.                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| Q3(a)       | What is the need of parallel operation of synchronous generator? What are the conditions to be satisfied for connecting two generators in parallel? What is the way of changing the load shared between the two generators?                                                                                                                                                                                                                                                                                                                     | 03+03+02      |

| (b)         | Two similar alternators operating in parallel have the following data:  Alternator 1 – Capacity 2 MW, frequency drops from 50 Hz at no load to  48.0 Hz at full load  Alternator 2 – Capacity 2 MW, frequency drops from 50.5 Hz at no load  to 48.5 Hz at full load.  Prime mover speed regulation is linear.  (i) Calculate how a total load of 3.6 MW is shared by each alternator.  Also find the operating bus frequency at this load.  (ii) Compute the maximum load that these two units can deliver without overloading either of them. |               |

| Q4(a)       | What is Blondel's model for salient pole synchronous machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10            |

| (b)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| Q5(a) | What are the effects of variation of excitation on the operation synchronous motor. Draw and explain in brief the V-curves and inverted V- curves of synchronous motor.                                                                                                                                                                                                                                               | 10 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| (b)   | A synchronous generator supplying isolated load with constant field current.  Mechanical input to synchronous generator is increased; explain the effect on excitation voltage, armature voltage, armature current and power factor.                                                                                                                                                                                  | 10 |

| Q6(a) | Justify the locations of field winding and armature winding in case of synchronous machines.                                                                                                                                                                                                                                                                                                                          | 08 |

| (b)   | A 600 V, 6-pole, 3-phase, 50 Hz, star connected synchronous motor has a resistance and synchronous reactance of 0.4 $\Omega$ and 7 $\Omega$ respectively. It takes a current of 15 A at upf when operating with a certain field current. With the field current remaining constant, the load torque is increased until the motor draws a current of 50 A. Find the torque (gross) developed and the new power factor. | 12 |

| Q7(a) | Derive the relation of power developed by salient pole synchronous generator. Explain the significance of the reluctance power term.                                                                                                                                                                                                                                                                                  | 12 |

| (b)   | Discuss the location and purpose of damper winding in synchronous machine.                                                                                                                                                                                                                                                                                                                                            | 08 |

20/6/20/6

### Bharatiya Vidya Bhavan's

# Sardar Patel College of Engineering

(A Government Aided Autonomous Institute)

Munshi Nagar, Andheri (West), Mumbai – 400058.

End Semester Re-Exam (old)

November 2016

Max. Marks: 100

Class: T.Y.B.Tech. (Electrical)

Semester: V

Duration: 3.00 Hrs

Program: Electrical Engineering

Course Code: EE301

### **Instructions:**

1. Question No 1 is compulsory.

Master file.

2. Attempt any four questions out of remaining six.

Name of the Course: Electromagnetic fields and waves

3. Draw neat diagrams

4. Assume suitable data if necessary

| Question |                                                                                                     | Maximum |

|----------|-----------------------------------------------------------------------------------------------------|---------|

| No.      |                                                                                                     | Marks   |

| Q1       | Attempt any four:                                                                                   | 20      |

|          | a) State and explain Gauss's law.                                                                   |         |

|          | b) State and explain Stoke's theorem.                                                               |         |

|          | c) Four point charges, each 20 $\mu$ C, are on the x and y axes at $\pm 4 m$ .                      |         |

|          | Find the force on a 100 $\mu$ C point charge at (0,0,3) m.                                          |         |

|          | d) In a cylindrical co-ordinates a vector field is given by,                                        |         |

|          | $\bar{A} = r \sin \emptyset \bar{a}_r + r^2 \cos \emptyset \bar{a}_\emptyset + 2re^{-5z} \bar{a}_z$ |         |

|          | Find div. A at $\left(\frac{1}{2}, \frac{\pi}{2}, 0\right)$ .                                       |         |

|          | e) State and explain Amperes circuital law.                                                         |         |

|          | f) What is Biot-Savart law? Use Ampere's circuital law to obtain H                                  |         |

|          | due to infinitely long, straight filament of current I.                                             |         |

| Q2(a)    | Describe applications of Gauss's law.                                                               | 10      |

| (b)      | Find the work done in moving a point charge $Q = -20 \mu\text{C}$ from                              | 05      |

|          | origin to (4,2,0) m in the field                                                                    |         |

|          | $E = 2(x+4y)a_z + 8xa_v (V/m)$                                                                      |         |

|          | Along the path $x^2 = 8y$ .                                                                         |         |

|          | Along the path $x = \delta y$ .                                                                     |         |

| (c)      | Determine the flux crossing a 1 mm by 1mm area on the surface of                                    | 05      |

|          | cylindrical shell at $r = 10 m$ , $z = 2 m$ , $\emptyset = 53.2^{\circ}$ if,                        |         |

|          | $\overline{D} = 2x\overline{a}_x + 2(1-y)\overline{a}_y + 4z\overline{\overline{a}}_z$              |         |

|          | At point P (see fig. 1)                                                                             |         |

|        | Fig. 1                                                                                                                                                                                                                                     |    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Q3(a)  | State Maxwell's equation for static fields. Explain how they are modified for time varying electric and magnetic fields.                                                                                                                   | 10 |

| (b)    | Given, $\overline{D} = D_m Sin(\omega t + \beta z)\overline{a_x}$ in free space. Find E, B and H. Sketch E and H at t=0                                                                                                                    | 05 |

| (c)    | Given that $D = \frac{5r^2}{4} a_r (C/m^2)$ in spherical coordinates, evaluate both sides of the divergence theorem for volume enclosed by $r = 4$ m and $\theta = \frac{\pi}{4}$ (see Fig. 2) $\oint D. ds = \int (\nabla . D) dv$ Fig. 2 | 05 |

| Q4(a)  | Starting with Ampere's law, derive Maxwell's equation in integral form. Obtain the corresponding relation by applying the Stoke's theorem.                                                                                                 | 08 |

| (b)    | What is coulombs law? Charge is distributed uniformly along an infinite straight line charge $\rho_l$ . Develop the expression for E at point P.                                                                                           | 08 |

| (c)    | Find the magnitude of $D$ , $P$ and $\epsilon_r$ for a dielectric material in which $E=0.15MV/m$ and $X_e=4.25$ .                                                                                                                          | 04 |

| Q5 (a) | Derive an expression for potential energy stored in static electric field of n point charges.                                                                                                                                              | 10 |

| (b)    | Two parallel conducting disks in Fig.3 are separated by 5mm and contain a dielectric for which $\epsilon_r=2.2$ . Determine the charge density on disk.                                                                                    | 05 |

|       | V=100 V<br>Fig. 3                                                                                                                                                                                        |    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| (c)   | Given $\bar{A} = 5\sin\theta \bar{a_{\theta}} + 5\sin\theta \bar{a_{\theta}}$ , Find $\nabla A$ at $(0.5, \pi/4, \pi/4)$                                                                                 | 03 |

| (d)   | Find the angle between $A = (5.8  \bar{a}_y + 1.55 \bar{a}_z)$ and $B = (-6.93 \bar{a}_y + 4.0 \bar{a}_z)$ using both dot product and cross product.                                                     | 02 |

| Q6(a) | Derive Poisson's and Laplace's equation.                                                                                                                                                                 | 08 |

| (b)   | Given that $\overline{E_1}=2\overline{a_x}-3\overline{a_y}+5\overline{a_2}$ V/m at the charge free dielectric interface of Fig. 4. Find $D_2$ and angle $\theta_1$ and $\theta_2$ .                      | 06 |

| (c)   | Identical charges of $Q(C)$ are located at the eight corners of a cube with side of $l$ meter show that coulombs force on each charge has magnitude $\left(\frac{3.29Q^2}{4\pi\epsilon_0 l^2}\right)N$ . | 06 |

| Q7(a) | Write short note on  1. Wave Equations 2. Reflected waves and intrinsic impedance for various materials.                                                                                                 | 10 |

| (b)   | Find the voltage across each dielectric in the capacitor shown in Fig. 5 when the applied voltage is 150 V.  Fig. 5                                                                                      | 04 |

| (e)   | The amplitude of $E^i$ in free space (Region 1) at the interface with region 2 is 1.0 V/m. If $H_0^r = -1.41 \times 10^{-3}$ A/m, $\epsilon_{r2} = 18.5$ and $\sigma_2 = 0$ , Find $\mu_{r2}$ .          | 06 |

16/2016

## Bharatiya Vidya Bhavan's

## Sardar Patel College of Engineering

(A Government Aided Autonomous Institute) Munshi Nagar, Andheri (West), Mumbai – 400058.

Re-Exam June 2016

Max. Marks: 100

Class: T.E. Semester: V

Name of the Course: Control System I

Q. P. Code:

Duration: Three Hours Program: Electrical Course Code: EE302

Master file.

#### Instructions:

1. Question No. 1 is compulsory.

2. Answer any four questions from remaining six.

3. Keep answers to the point.

4. Make suitable assumptions if required and justify the same.

| Question<br>No |                                                                                                                                                                                          | Maximum<br>Marks | Course<br>Outcome<br>Number |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------|

|                |                                                                                                                                                                                          |                  |                             |

| Q1a            | Derive an expression for peak overshoot for a typical second order system for unit step input                                                                                            | 05               | 1                           |

| Q1b            | Draw the signal flow graph of the following                                                                                                                                              | 05               | 1,2                         |

| Q1c            | Define notions of stability i.e. Bounded input bounded output and asymptotic. Determine if following systems are stable or unstable. $G(s) = \frac{1}{s}  and  G(s) = \frac{1}{s^2 + 1}$ | 05               | 1,,2                        |

| Q1d            | Define the following terms in context of root locus                                                                                                                                      |                  |                             |

|     | <ul> <li>a. Root Locus.</li> <li>b. Breakaway points</li> <li>c. Angle of Departure and Angle of Arrival</li> <li>d. Asymptotes and Centroid</li> <li>e. Angle and magnitude criterion ( write only expressions)</li> </ul>                                                               | 05 | 1,2  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|

|     |                                                                                                                                                                                                                                                                                           |    |      |

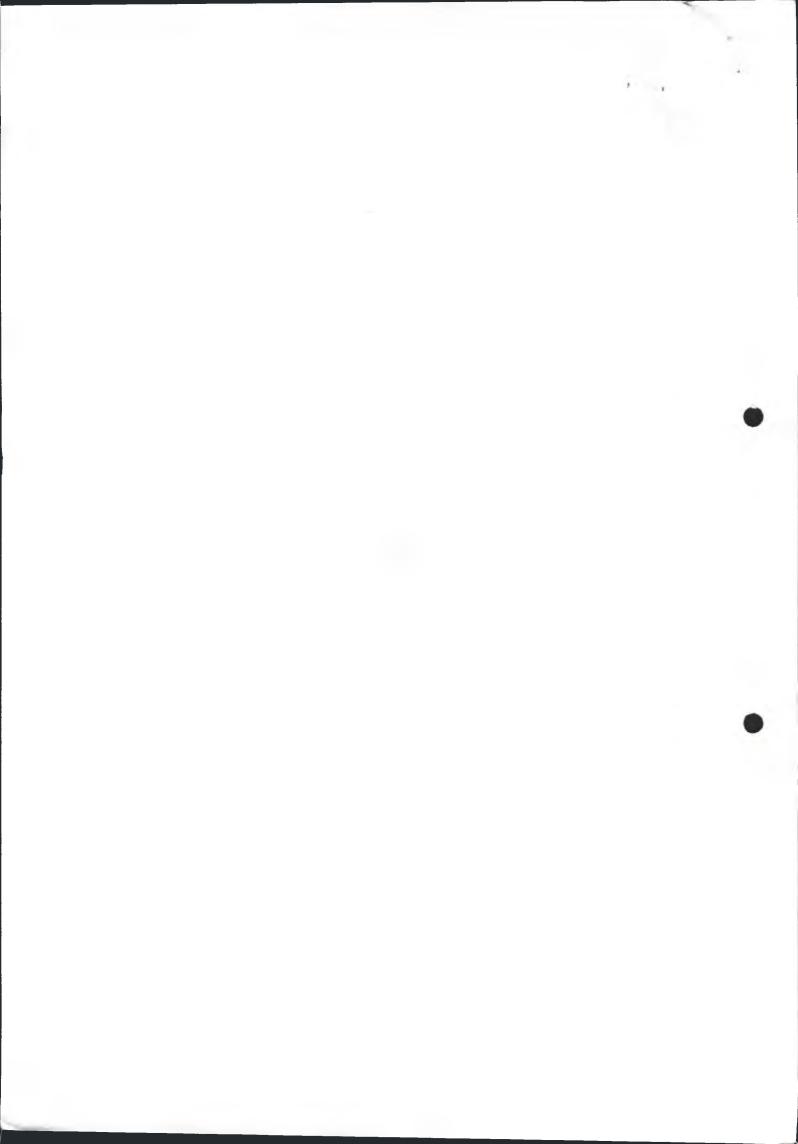

| Q2a | Reduce the block diagram shown in Fig. 1 to a single block $T(s) = \frac{C(s)}{R(s)}.$                                                                                                                                                                                                    | 10 | 1,3  |

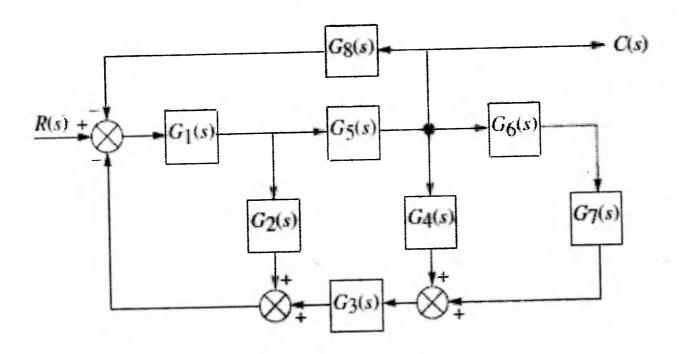

| Q2b | Find C(s)/R(s) by using Mason's gain formula for the Signal Flow Graph (SFG) shown in Fig. 2.                                                                                                                                                                                             | 10 | 2,3. |

| Q3a | The open loop transfer function of a unity feedback system is given by $G(s) = \frac{K}{s(Ts+1)}$ Where K and T are positive constants. By what factor should the value of gain "K" be reduced so that the peak overshoot of unit-step response of the system is reduced from 75% to 25%? | 14 | 2,3  |

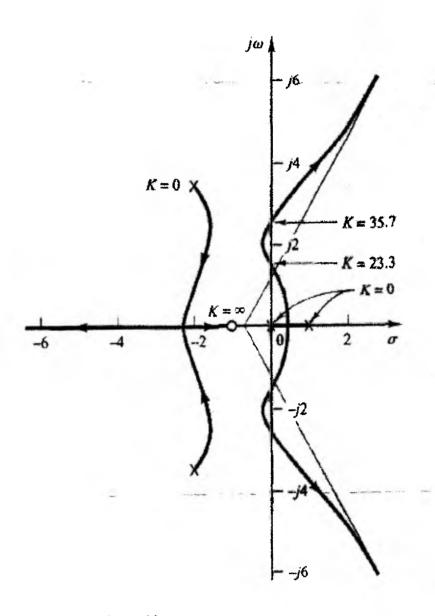

| Q3b | For the root locus plot shown in Fig.3 Mention the value/range of the gain K for which.  1. Closed loop system is stable.  2. Closed loop system is unstable.                                                                                                                             | 06 | 2,3  |

| Q4a | Determine the stability of the following transfer function by using Rouths criterion. $T(s) = \frac{84}{s^3 + 5s^2 + 12s^6 + 25s^5 + 45s^4 + 50s^3 + 82s^2 + 60s + 84}$                                                                                                                   | 10 | 1    |

| Q4b | b) Natural and damped frequency of oscillations c) Settling, Peak and Rise time d) Percentage Overshoot e) Steady state error for unit step, unit ramp and unit parabolic input for the second order system shown below. $T(s) = \frac{1.05 \times 10^7}{s^2 + 1.6 \times 10^3 s + 1.05 \times 10^7}$                            | 10    | 1,2   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|

| Q5  | Consider the unity feedback system with $G(s) = \frac{K}{(s+3)(s+5)}$ a. Show that the system cannot operate with a settling time of <b>0.667 second</b> and a percentage overshoot of 1.5% with simple gain adjustment. b. Design a lead compensator so that the system meets the transient response characteristics of part a. | 10+10 | 1,2,3 |

|     |                                                                                                                                                                                                                                                                                                                                  |       |       |

| Q6a | A negative unity feedback system with forward path transfer function $G(s) = \frac{K(s+\alpha)}{(s+\beta)}$ has to be designed such that  (i) the steady-state position error for a ramp input is 0.1 and (ii) closed-loop poles will be located at $-1 \pm j$ Find $K$ , $\alpha$ and $\beta$ to meet the specifications.       | 15    | 1,2,3 |

| <b>Q</b> 7 | For the unity feedback system with $G(s) = \frac{K}{(s+1)(s+4)}$ Design a PID controller that will yield a peak time of 1.047 seconds and a damping ratio of 0.8, with zero error for step input. | 20 |     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| Q6b        |                                                                                                                                                                                                   | 05 | 1,2 |

|            | b) Pole/Zero plot of five systems i.e. A,B,C,D and E are shown in below given figure. Comment on the stability of each system.                                                                    |    |     |

Fig. 1 Block diagram for Q2 a)

Fig. 2 SFG for Q2 b)

Fig. 3 Block diagram for Q2 b)